Designers of test and measurement solutions, such as automotive test beds and hardware-in-the-loop (HIL) subsystems, are increasingly challenged to find the optimal balance of high performance with lower latency and wider bandwidth. At the same time, they need flexibility and reconfigurability to support rapidly changing system requirements and to service a breadth of use cases.

Traditionally, meeting these requirements—while maintaining precision AC and DC performance as sample rates increase—requires significant design/debug time and effort. This effort increases with any redesign when changing components to accommodate changes in test-bed and instrumentation objectives.

A better alternative is a platform approach based on devices that are programmable, reconfigurable, and reusable. These “anchor” parts establish a baseline of performance that can be used—and reused—across variations of a single type of application or even multiple disparate applications.

This article introduces the Analog Devices AD3552R digital-to-analog converter (DAC) as an example of how programmable components can accomplish designers’ objectives to create a scalable, easily optimized, reconfigurable signal-chain platform. Evaluation boards and LTspice support are discussed to help designers get started. Also introduced is the highly integrated ADAQ23878 analog-to-digital converter (ADC) which, together with the AD3552R, can form two critical and complementary anchor parts for a platform-based approach.

Integration and programmability simplify designs

As test system requirements change, the traditional and often successful techniques that have been used to maximize precision and minimize error, although with added design and component cost, are:

- Choosing “better” components such as resistors with tighter tolerance or lower temperature coefficient so as to minimize inadequacies both in initial performance and over time and temperature.

- Using topologies that support self-cancelation of unavoidable errors to a large extent, such as matched resistors and differential circuits or the classic Wheatstone bridge.

- Providing initial and ongoing calibration through the use of a “golden” component, such as a precision voltage reference to which all other key voltages can be compared.

Success using these techniques becomes more challenging for test system designers when the application requires high update rates for the ADC and the DAC.

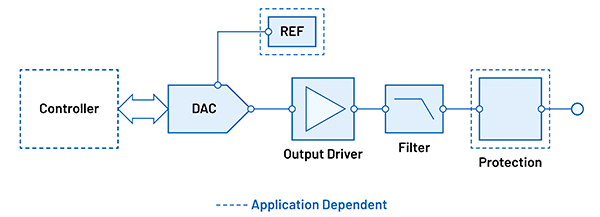

To eliminate many of these challenges, a programmable, platform-based approach offers a better option by minimizing—or even eliminating—the need to design “from scratch” for the initial project, and as requirements change. The approach also ensures a consistent means of evaluating and simulating a design. A critical element of this programmable approach is the DAC (Figure 1).

DAC performance and capabilities are increasingly being “stressed” by test-and-control applications that demand precision, low latency, and fast settling across a wide voltage range. They also demand flexibility and need to be easily reconfigured without going through a full or complicated redesign, and requalification cycle. These applications include Hardware in the Loop, electron scanning microscopes, electrical impedance tomography or mass spectrometry to name a few. Fast update is useful to speed up scanning applications while low latency is useful to increase close-loop bandwidth in applications where an ADC is used to provide feedback.

The ADI AD3552R can address performance objectives as it is a 16-bit, 33 million updates per second (MUPS), multi-span, dual-output SPI DAC (Figure 2). In addition to basic performance attributes, another advantage of the AD3552R is the ease with which it can be reconfigured to meet new or changing project objectives. This reconfigurability includes an assurance that it will meet those objectives with a high level of confidence, rather than bring new and unwanted “surprises.”

The AD3552R is available in a 5 millimeter (mm) × 5 mm LFCSP package and operates with a fixed 2.5-volt reference but can be configured via software for multiple voltage-span output ranges. It also enables an optimal balance of performance, precision, speed, and flexibility.

The device incorporates three drift-compensating feedback resistors to support the external transimpedance amplifier (TIA) that scales the output voltage. Offset and gain scaling registers allow for the generation of multiple output span ranges, such as 0 to 2.5 volts, 0 to 5 volts, 0 to 10 volts, −5 to +5 volts, and −10 to +10 volts, as well as custom intermediate ranges with full 16-bit resolution.

Further, to address the well-known “speed versus precision” dilemma, the AD3552R DAC can operate in Fast Mode for maximum update rate, or Precision Mode for highest precision and maximum accuracy across temperature. In the Fast Mode, the DAC data is loaded as a 16-bit word, resulting in a single-channel update rate of 33 MUPS. In contrast, in Precision Mode, data is written as a 24-bit word, resulting in a single-channel update rate of 22 MUPS.

For those applications which require lower noise density along with faster settling time, and which can accept higher power consumption, the AD3552R supports combining of the two DAC channels to produce a single output (Figure 3). Both DACs can be updated simultaneously with the same code without penalizing the update rate.

There’s also flexibility in the device’s SPI interface, as it can be configured in single SPI (classic SPI), dual SPI, synchronous dual SPI, and quad SPI modes, with single data rate (SDR) or double data rate (DDR) operation, and with logic levels from 1.2 to 1.8 volts. Further, as data integrity is also an ongoing and increasing concern, the device can be enabled to incorporate a cyclic redundancy check (CRC). Multiple error checkers have also been integrated to detect VREF failures or memory map corruption.

Simulation models speed configuration, instill confidence

Although the AD3552R is a wideband precision device, there will always be tradeoffs among its many user-programmable parameters. To accelerate understanding of the impact of these design options and help designers get started, it is supported by evaluation boards as well as LTspice for assessing noise, transient analysis, AC simulation, and other parameters. This simplifies latency/performance optimization, so designers don’t have to set parameter values or make compromises without credible data.

The ability to use LTspice in the signal chain brings all of its elements together so users can clearly understand the complete signal chain performance. This is especially important as the AD3552R offers:

- Ten current ranges; resulting from the combination of digitally configured gain-scaling values.

- Three transimpedance-gain values; resulting from the connection of one of the feedback resistors.

- A total of 511 digitally configured DC offset values.

That’s a total of 15,330 combinations, clearly beyond the scope of any “hands-on” breadboarding approach or even selective manual assessment.

The LTspice model for the AD3552R updates the traditional analog-output-focused DAC models with a more digitally focused simulation. The functionality of some registers in the model—in particular those related to digital gain scaling and DC offset—can be simulated, and the model is also able to reproduce dynamic and noise performance with high fidelity. Among the AD3552R performance characteristics which the LTspice software simulates are:

- Output Range Simulation: The DC sweep simulation is useful to confirm the span of the output voltage for a given configuration of parameters. It also accounts for the limitations imposed by the operational amplifier’s headroom (top of range) and footroom (bottom), making it easy to anticipate any saturation of the output signal.

- Step Response Tuning: The transient simulation with a step waveform is useful to adjust the value of the feedback capacitor and the output filter of the TIA to achieve the desired rise time, settling time, and overshoot, and it can be combined with a parametric sweep to find the optimal values of the parts. The simulation also accounts for the drive capability of the amplifier and DAC to estimate the slew rate and rise time of the signal. (Note that this value is a starting point because the simulation circuit does not include the parasitic effects of the board and the packages of the parts.)

- AC Bandwidth Simulation: The AC Sweep simulation is useful to adjust the values of the feedback capacitor and the output filter of the TIA in applications where the output signal is harmonic.

- Noise Density Simulation: This enables prediction of the noise density at the output of the DAC and the TIA, both in the 1/f region and the thermal noise region. The LTspice model of the AD3552R captures the variation of noise density with the code, and also accounts for the gain of the TIA, which scales up the noise at the output of the current DAC.

For more on LTspice, see “How to use LTspice to Determine Photo Sensing Noise Performance During Sensitive Instrument Design” and the AD3552R LTspice model.

Practice, test, with real hardware

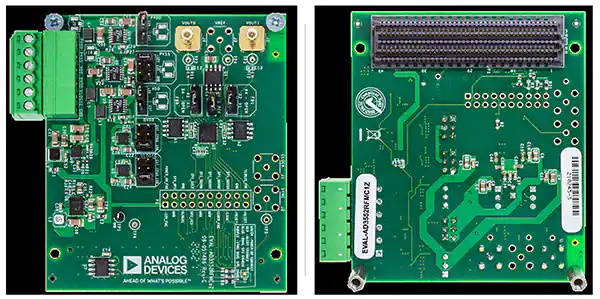

Simulations are extremely useful and necessary, but as any experienced engineer knows, they cannot fully replace a real-world evaluation, especially when factors such as parasitics outside the device can affect performance. For the AD3552R, this need is met using the EVAL-AD3552RFMCxZ, which is available in two variants: the EVAL-AD3552RFMC1Z for higher speed, and the EVAL-AD3552RFMC2Z for higher precision (Figure 4).

The software for the board uses ADI’s “Analysis, Control, Evaluation” (ACE) package, a desktop application that allows the evaluation and control of multiple evaluation systems across ADI’s product portfolio. The application consists of a common framework and individual component-specific plug-ins.

For the AD3552R, ACE has several views to control different aspects of the DAC. When a view is first opened, it creates a new tab at the top of the main window. The AD3552R plug-in produces a hierarchy of views: Board View, a Chip View, a Memory Map view, and an Analysis View that combines a Waveform Generator view and a Vector Generator view (Figure 5).

- The Board View displays a simplified diagram of the evaluation board, including some relevant connectors and the interconnection between chips.

- The Chip View displays a simplified internal diagram of the chip showing the interface logic, the DAC cores, the precision feedback resistors, and the relevant pins for those blocks.

- The Memory Map view displays the entire configuration space of the AD3552R; this space can be displayed as a list of registers or as a list of bit fields.

- The Waveform Generator view allows assigning vectors to the channels and starting or stopping waveform generation.

- The Vector Generator view allows defining or loading of waveforms that can later be assigned to the DAC channels.

Using the evaluation board and ACE software, users of the AD3552R can confirm the decisions they made via the LTspice simulator and adjust as needed. Users can also exercise the device with its many registers and programmable functions and features.

Explore other data acquisition options

The options for highly programmable components that can be used to create scalable, easily optimized, reconfigurable signal-chain platforms are not limited to devices such as the AD3552R.

For example, Analog Devices’ ADAQ23878 is an 18-bit, 15-MSPS µModule pin-strappable solution ADC. This high-speed data-acquisition solution simplifies and accelerates the development cycle of precision measurement systems by eliminating much of the design burden of component selection, optimization, and layout through the use of an off-the-shelf device.

Using system-in-package (SIP) technology, the ADAQ23878 reduces end-system component count by combining multiple common signal processing and conditioning blocks in a single device. It includes a low-noise, fully differential ADC driver amplifier, a stable reference buffer, and a high-speed, 18-bit, 15 MSPS successive approximation register (SAR) ADC (Figure 6).

The ADAQ23878 also incorporates the critical passive components with superior matching and drift characteristics that come through the use of ADI’s iPassive technology, which minimizes temperature-dependent error sources for optimal performance. The small footprint of just 9 mm × 9 mm, with 0.8 mm pitch and a 100-ball CSP BGA package, enables smaller form factor instruments without sacrificing performance (Figure 7).

The system integration solves many design challenges while the device still provides the flexibility of a configurable ADC-driver feedback loop to allow gain or attenuation adjustments, as well as fully differential or single-ended-to-differential input.

For example, it can be the core of a complete flow cytometer (see, “Quickly Implement Flow Cytometer Designs Using High-Accuracy Data Acquisition Modules”), or a wide-range current measurement system with accuracy, bandwidth, and drift performance comparable to benchtop and rack-mount test equipment for a production test environment (Figure 8). At the same time, the solution is small enough to be incorporated into applications that need to be continuously monitored. The design features high-accuracy measurement of three current ranges using a combination of shunt resistors, onboard amplifiers, and the ADAQ23878 μModule.

Conclusion

Designers of test and measurement equipment require precision, performance, and flexibility, while also having the ability to readily reconfigure the basic design to service a wide breadth of use cases. As shown, components such as the AD3552R DAC feature many programmable parameters, allowing them to be quickly and easily tailored as needed. Together with the ADAQ23878 ADC and supported by tools such as LTspice and evaluation boards and software, the AD35525 plays a key role in a platform-based approach to test system design that provides the required flexibility and performance, while minimizing the time required for reconfiguration.

Authored Article by: