In a new era of computing driven by the convergence of 5G, machine learning and the internet of things (IoT), embedded developers need the richness of Linux-based operating systems. These must meet deterministic system requirements in ever lower power, thermally constrained design environments, all while addressing critical security and reliability requirements.

Traditional system-on-chip (SoC) field programmable gate arrays (FPGAs) blending reconfigurable hardware with Linux-capable processing on a single chip provide developers ideal devices for customisation, yet consume too much power, lack proven levels of security and reliability, or use inflexible and expensive processing architectures.

In response, Microchip Technology Inc., via its Microsemi Corporation subsidiary, has extended its Mi-V ecosystem by unveiling the architecture for a new class of SoC FPGAs that combine the industry’s lowest power mid-range PolarFire FPGA family with a complete microprocessor subsystem based on the open, royalty-free RISC-V instruction set architecture (ISA).

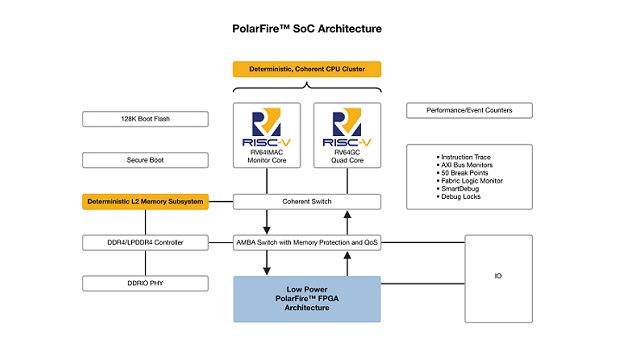

Announced at the RISC-V Summit in Santa Clara, California, Microchip’s new PolarFire SoC architecture brings real-time deterministic asymmetric multiprocessing (AMP) capability to Linux platforms in a multi-core coherent central processing unit (CPU) cluster. The PolarFire SoC architecture, developed in collaboration with SiFive, features a flexible 2 MB L2 memory subsystem that can be configured as a cache, scratchpad or a direct access memory.

“The PolarFire SoC architecture is a compelling combination of low power, security and reliability in a configurable device that brings real-time to Linux,” said Bruce Weyer, Vice President of the Programmable Solutions business unit at Microchip. “Coupled with our robust Mi-V RISC-V ecosystem and Microchip’s extensive portfolio of system solutions, the PolarFire SoC architecture gives customers an excellent platform to meet computing’s next great challenges.”

PolarFire SoC includes extensive debug capabilities including instruction trace, 50 breakpoints, passive run-time configurable Advanced eXtensible Interface (AXI) bus monitors and FPGA fabric monitors, and Microchip’s built-in two-channel logic analyser SmartDebug. The PolarFire SoC architecture includes reliability and security features such as single error correction and double error detection (SEC-DED) on all memories, physical memory protection, a differential power analysis (DPA) safe crypto core, defense-grade secure boot and 128Kb flash boot memory.

“As a fully customisable, programmable RISC-V platform, the PolarFire SoC architecture gives designers the freedom to create innovative Linux-based SoCs in novel and interesting ways tailored for their distinct, domain-specific requirements,” said SiFive CEO Naveed Sherwami. “By leveraging SiFive’s market-leading U54-MC CPU core complex, PolarFire SoC will enable designers to overcome the universal challenge of building real-time systems with predictable behaviours.”